# 18V, 2.5A, 1.4MHz Synchronous Step-Down DC/DC Converter

### **Description**

The FR9872 is a synchronous step-down DC/DC converter that provides wide 4.5V to 18V input voltage range and 2.5A continuous load current capability.

Fault protection includes cycle-by-cycle current limit, input UVLO, output over voltage protection and thermal shutdown. Besides, adjustable soft-start function prevents inrush current at turn-on. This device uses current mode control scheme that provides fast transient response. In shutdown mode, the supply current is about 10µA.

The FR9872 is available in SOP-8 (exposed pad) package, which provides a very compact system solution and good thermal conductance.

#### **Features**

- Wide Input Voltage from 4.5V to 18V

- 2.5A Output Current

- Adjustable Output Voltage from 0.925V to 14V

- •130mΩ Integrated Power MOSFET

- High Efficiency up to 93%

- Fixed 1.4MHz Switching Frequency

- Current Mode Operation

- Adjustable Soft-Start

- Cycle-by-Cycle Current Limit

- Input Under Voltage Lockout

- Over-Temperature Protection with Auto Recovery

- 10µA Shutdown Current

- Thermal Enhanced SOP-8 (Exposed Pad) Package

- RoHS Compliant

### **Applications**

- Set-Top-Box

- DVD,LCD Display

- OLPC, Netbook

- Distributed Power System

- Datacom, XDSL

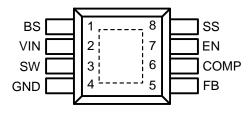

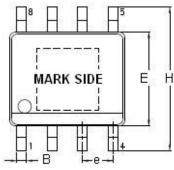

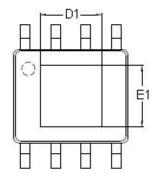

## **Pin Assignments**

SP Package (SOP-8 Exposed Pad)

Figure 1. Pin Assignment of FR9872

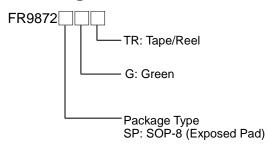

## **Ordering Information**

FR9872-1.3-MAR-2012

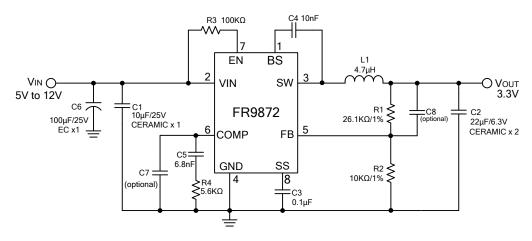

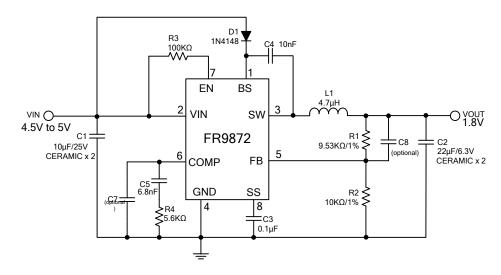

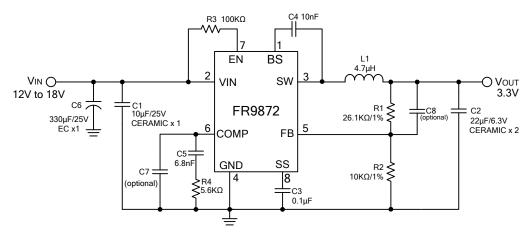

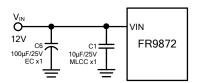

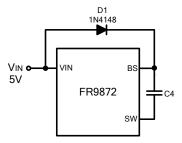

# **Typical Application Circuit**

Figure 2. Output 3.3V Application Circuit

Figure 3. Low Input Voltage Application Circuit

Figure 4. High Input Voltage Application Circuit

# **Functional Pin Description**

| Pin Name | Pin No.I | Pin Function                                                                                                                                                                   |  |  |  |  |  |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BS       | 1        | High Side Gate Drive Boost Input. A 10nF or greater capacitor must be connected from this pin to SW. It can boost the gate drive to fully turn on the internal high side NMOS. |  |  |  |  |  |

| VIN      | 2        | Power Supply Input Pin. Drive 4.5V to 18V voltage to this pin to power on this chip. Connect a $10\mu F$ ceramic bypass capacitors between VIN and GND to eliminate noise.     |  |  |  |  |  |

| sw       | 3        | Power Switching Output. It is the output pin of internal high side NMOS which is the switch to supply power.                                                                   |  |  |  |  |  |

| GND      | 4        | Ground Pin. Connect this pin to exposed pad.                                                                                                                                   |  |  |  |  |  |

| FB       | 5        | Voltage Feedback Input Pin. Connect FB and VOUT with a resistive voltage divider. This IC senses feedback voltage via FB and regulates it at 0.925V.                           |  |  |  |  |  |

| COMP     | 6        | Compensation Pin. This pin is used to compensate the regulation control loop. Connect a series RC network from COMP pin to GND.                                                |  |  |  |  |  |

| EN       | 7        | Enable Input Pin. This pin provides a digital control to turn the converter on or off. Connect to VIN with a $100K\Omega$ resistor for self-startup.                           |  |  |  |  |  |

| SS       | 8        | Soft-Start Input Pin. This pin controls the soft-start period. Connect a capacitor from SS to GND to set the soft start period.                                                |  |  |  |  |  |

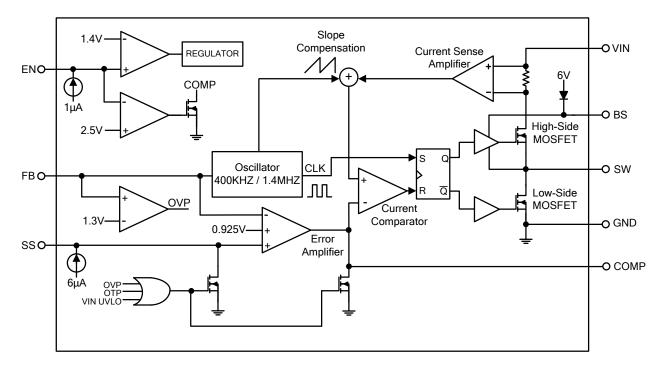

# **Block Diagram**

Figure 5. Block Diagram of FR9872

# **Absolute Maximum Ratings**

| • Supply Voltage (V <sub>IN</sub> )                                                                | 0.3V to +20V                   |

|----------------------------------------------------------------------------------------------------|--------------------------------|

| • SW Voltage VSW                                                                                   | -1V to V <sub>IN</sub> +0.3V   |

| • Boost Trap Voltage (VBS)                                                                         | $V_{sw}$ -0.3V to $V_{sw}$ +6V |

| All Other Pins Voltage                                                                             | -0.3V to +6V                   |

| Maximum Junction Temperature (T <sub>J</sub> )                                                     | +150°C                         |

| Storage Temperature (T <sub>S</sub> )                                                              | -65°C to +150°C                |

| • Lead Temperature (Soldering, 10sec.)                                                             | +260°C                         |

| <ul> <li>Power Dissipation @T<sub>A</sub>=25°C, (P<sub>D</sub>)</li> </ul>                         |                                |

| SOP-8 (Exposed Pad)                                                                                | · 1.25W                        |

| <ul> <li>Package Thermal Resistance, (θ<sub>JA</sub>)</li> </ul>                                   |                                |

| SOP-8 (Exposed Pad)                                                                                | - 50°C/W                       |

| <ul> <li>Package Thermal Resistance, (θ<sub>JC</sub>)</li> </ul>                                   |                                |

| SOP-8 (Exposed Pad)                                                                                | · 15°C/W                       |

| Note 4 to Observe the considerable and listed condenses the Manifestory Define all consequences of | Access to the Access           |

Note 1: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

# **Recommended Operating Conditions**

| • Supply Voltage (Vin)             | +4.5V to +18V   |

|------------------------------------|-----------------|

| Output Voltage (V <sub>OUT</sub> ) | +0.925V to +14V |

| Operation Temperature Range        | -40°C to +85°C  |

### **Electrical Characteristics**

(V<sub>IN</sub>=12V, T<sub>A</sub>=25°C, unless otherwise specified.)

| Parameter                                       | Conditions                                   | Min | Тур   | Max  | Unit          |

|-------------------------------------------------|----------------------------------------------|-----|-------|------|---------------|

| V <sub>IN</sub> Input Supply Voltage (Note 2)   |                                              | 4.5 |       | 18   | ٧             |

| V <sub>IN</sub> Supply Current                  | V <sub>EN</sub> = 1.8V                       |     | 1.1   |      | mA            |

| V <sub>IN</sub> Shutdown Supply Current         | V <sub>EN</sub> = 0V                         |     | 10    | 15   | μA            |

| Feedback Voltage                                | 4.5V≦VIN≦18V                                 | 0.9 | 0.925 | 0.95 | V             |

| Feedback OVP Threshold Voltage                  |                                              |     | 1.3   |      | V             |

| High-Side MOSFET RDS(ON) (Note 3)               |                                              |     | 120   |      | mΩ            |

| Low-Side MOSFET RDS(ON) (Note 3)                |                                              |     | 80    |      | mΩ            |

| High-Side MOSFET Leakage Current                | $V_{EN} = 0V$ , $V_{SW} = 0V$                |     |       | 10   | μA            |

| High-Side MOSFET Current Limit (Note 3)         | Minimum Duty                                 |     | 5     |      | А             |

| Low-Side MOSFET Current Limit (Note 3)          |                                              |     | 3     |      | А             |

| Current sense to COMP Transconductance (Note 3) |                                              |     | 6.1   |      | A/V           |

| Error Amplifier Transconductance (Note 3)       | $\Delta I_{COMP} = \pm 10 \mu A$             |     | 1800  |      | μ <b>A</b> /V |

| Error Amplifier Voltage Gain (Note 3)           |                                              |     | 400   |      | V/V           |

| Oscillation frequency                           |                                              |     | 1.4   |      | MHz           |

| Short Circuit Oscillation Frequency             | V <sub>FB</sub> = 0V                         |     | 400   |      | KHz           |

| Maximum Duty Cycle                              | V <sub>FB</sub> = 0.8V                       |     | 80    |      | %             |

| Minimum On Time (Note 3)                        |                                              |     | 120   |      | ns            |

| Input UVLO Threshold                            | V <sub>IN</sub> Rising                       |     | 4.4   |      | V             |

| Under Voltage Lockout Threshold Hysteresis      |                                              |     | 400   |      | mV            |

| Soft-Start Current                              | V <sub>COMP</sub> = 0V, V <sub>SS</sub> = 0V |     | 6     |      | μA            |

| Soft-Start Period                               | C <sub>SS</sub> = 0.1µF                      |     | 15    |      | ms            |

| EN Lockout Threshold Voltage                    |                                              | 2.3 | 2.5   | 2.7  | V             |

| EN Shutdown Threshold Voltage                   |                                              | 1.1 | 1.4   |      | V             |

| Thermal Shutdown Threshold (Note 3)             |                                              |     | 160   |      | °C            |

Note 2 : When  $V_{\text{IN}}$  = 4.5V,  $V_{\text{OUT}}$  = 3.3V, maximum load current is about 1A.

Note 3: Not production tested.

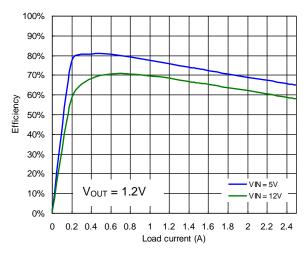

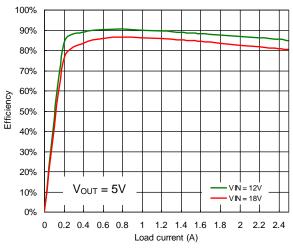

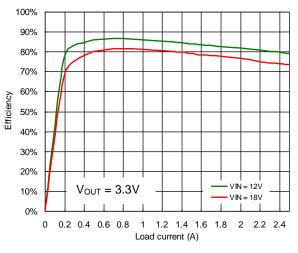

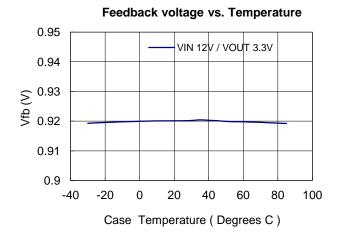

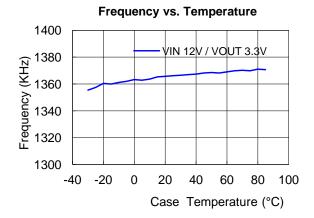

# **Typical Performance Curves**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $C1 = 10 \mu F$  x 1,  $C6 = 100 \mu F$  x 1,  $C2 = 22 \mu F$  x 2,  $L1 = 4.7 \mu H$ ,  $TA = +25 ^{\circ}C$ , unless otherwise noted.

Figure 6. Efficiency vs. Loading

Figure 8. Efficiency vs. Loading

Figure 7. Efficiency vs. Loading

Figure 9. Feedback Voltage vs. Temperature

Figure 10. Frequency vs. Temperature

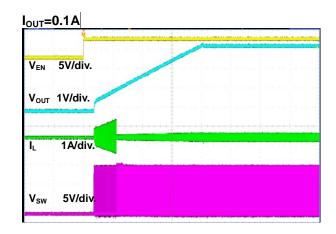

# **Typical Performance Curves (Continued)**

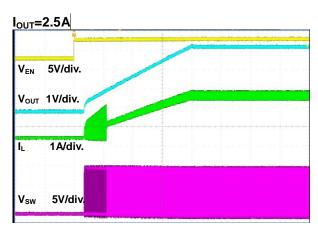

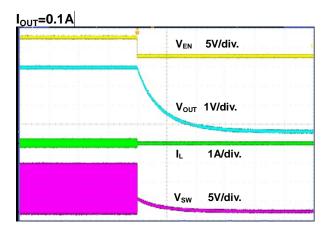

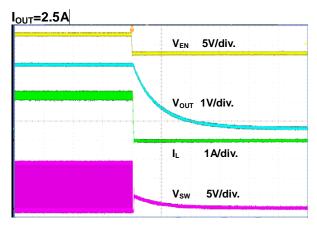

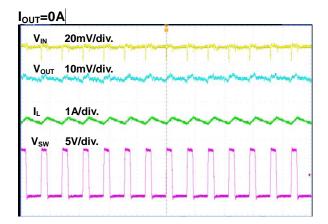

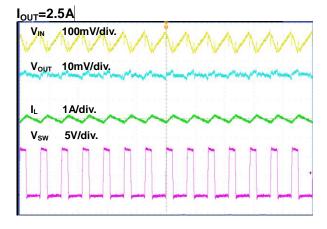

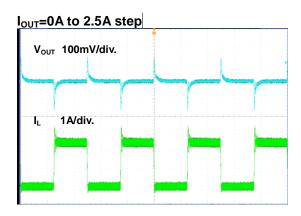

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $C1 = 10 \mu F$  x 1,  $C6 = 100 \mu F$  x 1,  $C2 = 22 \mu F$  x 2,  $L1 = 10 \mu H$ ,  $TA = +25 ^{\circ}C$ , unless otherwise noted.

Figure 11. Startup Through Enable Waveform

Figure 12. Startup Through Enable Waveform

Figure 13. Shutdown Through Enable Waveform

Figure 14. Shutdown Through Enable Waveform

Figure 15. Steady State Waveform

Figure 16. Steady State Waveform

# **Typical Performance Curves (Continued)**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $C1 = 10 \mu F$  x 1,  $C6 = 100 \mu F$  x 1,  $C2 = 22 \mu F$  x 2,  $L1 = 10 \mu H$ ,  $TA = +25 ^{\circ}C$ , unless otherwise noted.

Figure 17. Load Transient Waveform

### **Function Description**

The FR9872 is a 1.4MHz constant frequency current mode step-down synchronous DC/DC converter. It regulates input voltage from 4.5V to 18V, down to output voltage as low as 0.925V, and provides 2.5A of continuous load current.

#### **Control Loop**

During normal operation, the output voltage is sensed at FB pin by a resistive voltage divider and amplified through the error amplifier. The voltage of error amplifier output pin -- COMP is compared to the switch current to control the RS latch. At each cycle, the high side NMOS will be turned on when the oscillator sets the RS latch and turned off when current comparator resets the RS latch. When the load current increases, the FB pin voltage will drop below 0.925V, and it will cause the COMP voltage increasing until average inductor current arrives at new load current.

#### **Enable**

The FR9872 EN pin provides digital control to turn on/off the regulator. When the voltage of EN exceeds the threshold voltage, the regulator will start the soft start function. If the EN pin voltage is below the threshold voltage, only the bandgap voltage will be alive. If the EN pin voltage is below the shutdown threshold voltage, the regulator will be disabled and turn into the shutdown mode.

#### **Output Over Voltage Protection**

When the FB pin voltage exceeds 1.3V, the output over voltage protection function will discharge the COMP pin to GND and turn the high side MOSFET off.

#### Input Under Voltage Lockout

When the FR9872 is power on, the internal circuits will be held inactive until  $V_{\text{IN}}$  exceeds the input UVLO threshold voltage. And the regulator will be disabled when  $V_{\text{IN}}$  is below the input UVLO threshold voltage. The hysteretic of the UVLO comparator is 400 mV.

#### **Short Circuit Protection**

The FR9872 provides short circuit protection function to prevent the device damaged from short condition. When the output is short to ground, the oscillator frequency will be reduced to prevent the inductor current increasing beyond the current limit. In the meantime, the current limit will also be reduced to lower the short current. Once the short condition is removed, the frequency and current limit will return to normal.

#### **Over Temperature Protection**

The FR9872 incorporates an over temperature protection circuit to protect itself from overheating. When the junction temperature exceeds the thermal shutdown threshold temperature, the regulator will be shut down and re-enabled when the IC junction temperature drops 30°C (typ).

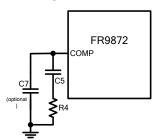

#### Compensation

The stability of the feedback circuit is controlled by COMP pin. The compensation value of the application circuit is optimized for particular requirements. If different conversions are required, some of the components may need to be changed to ensure stability.

FR9872-1.3-MAR-2012

### **Application Information**

#### **Output Voltage Setting**

The output voltage  $V_{\text{OUT}}$  is set by using a resistive divider from the output to FB. The FB pin regulated voltage is 0.925V. Thus the output voltage is:

$$V_{OUT} = 0.925 \times \left(1 + \frac{R1}{R2}\right) V$$

R2 recommended value is  $10k\Omega$ , so R1 is determined by:

R1=10.81×

$$(V_{OUT}$$

-0.925)k $\Omega$

Table 1 lists recommended values of R1 and R2 for most used output voltage.

Table 1 Recommended Resistance Values

| V <sub>out</sub> | R1     | R2   |

|------------------|--------|------|

| 12V              | 121kΩ  | 10kΩ |

| 5V               | 44.2kΩ | 10kΩ |

| 3.3V             | 26.1kΩ | 10kΩ |

| 2.5V             | 16.9kΩ | 10kΩ |

| 1.8V             | 9.53kΩ | 10kΩ |

Place resistors R1 and R2 close to FB pin to prevent stray pickup.

#### Input Capacitor Selection

The use of the input capacitor is controlling the input voltage ripple and the MOSFETS switching spike voltage. Because the input current to the step-down converter is discontinuous, the input capacitor is required to supply the current to the converter to keep the DC input voltage. The capacitor voltage rating should be 1.25 to 1.5 times greater than the maximum input voltage. The input capacitor ripple current RMS value is calculated as:

$$I_{IN(RMS)} = I_{OUT} \times \sqrt{D \times (1-D)}$$

Where D is the duty cycle of the power MOSFET.

A low ESR capacitor is required to keep the noise minimum. Ceramic capacitors are better, but tantalum or low ESR electrolytic capacitors may also suffice. When using tantalum or electrolytic capacitors, a  $0.1\mu F$  ceramic capacitor should be placed as close to the IC as possible.

It is recommended that the input EC capacitor could be added for applications if the FR9872 suffers high spike input voltage (ex. hot plug test). It can eliminate the spike voltage induced the IC damaged from high input voltage stress (see Note1).

Table 2 lists recommended values of C1 and C6 for most used input voltage.

**Table 2 Recommended Capacitor Values**

| V <sub>IN</sub> | C1       | C6        |  |

|-----------------|----------|-----------|--|

| 5V              | 10μF × 2 |           |  |

| 12V             | 10μF × 1 | 100μF × 1 |  |

| 18V             | 10μF × 1 | 330µF × 1 |  |

#### **Output Capacitor Selection**

The output capacitor is used to keep the DC output voltage and supply the load transient current. Low ESR capacitors are preferred. Ceramic, tantalum or low ESR electrolytic capacitors can be used depending on the output ripple requirements. Add a 100µF or 470µF Low ESR electrolytic capacitor when operating in high input voltage range ( $V_{\text{IN}} > 20V$ ). It can improve the device's stability. The output ripple voltage  $\Delta V_{\text{OUT}}$  is described as:

$$\Delta I = \frac{V_{OUT}}{F_{OSC} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

$$\Delta V_{OUT} = \Delta I \times \left(R_{ESR} + \frac{1}{8 \times F_{OSC} \times C_{OUT}}\right)$$

Where  $\Delta I$  is the peak-to-peak inductor ripple current,  $F_{OSC}$  is the switching frequency, L is the inductance value,  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage,  $R_{ESR}$  is the equivalent series resistance value of the output capacitor, and the  $C_{OUT}$  is the output capacitor. When using the ceramic capacitors, the  $R_{ESR}$  can be ignored and the output ripple voltage  $\Delta V_{OUT}$  is shown as:

$$\Delta V_{OUT} = \frac{\Delta I}{8 \times F_{OSC} \times C_{OUT}}$$

When using tantalum or electrolytic capacitors, typically 90% of the output voltage ripple is contributed by the ESR of output capacitors. The output ripple voltage  $\Delta V_{\text{OUT}}$  can be estimated as:

$$\Delta V_{OUT} = \Delta I \times R_{ESR}$$

### **Application Information (Continued)**

#### **Output Inductor Selection**

The output inductor is used for storing energy and filtering output ripple current. But the trade-off condition often happens between maximum energy storage and the physical size of the inductor. The first consideration for selecting the output inductor is to make sure that the inductance is large enough to keep the converter in the continuous current mode. That will lower ripple current and result in lower output ripple voltage. A good rule for determining the inductance is setting the peak-to-peak inductor ripple current  $\Delta I$  almost equal to 30% of the maximum load current. Then the minimum inductance can be calculated with the following equation:

$$\Delta I = 0.3 \times I_{OUT(MAX)}$$

$$L \ge (V_{IN} - V_{OUT}) \times \left( \frac{V_{OUT}}{F_{OSC} \times \Delta I \times V_{IN}} \right)$$

Where V<sub>IN</sub> is the maximum input voltage.

#### **Compensation Components Selection**

Select the appropriate compensation value by following procedure:

1. Calculate the R4 value with the following equation:

$$R4 < \frac{2\pi \times C_{OUT} \times 0.1 \times F_{OSC} \times V_{OUT}}{G_{EA} \times G_{CS} \times V_{REF}}$$

where  $G_{\text{EA}}$  is the error amplifier voltage gain, and  $G_{\text{CS}}$  is the current sense gain.

2. Calculate the C5 value with the following equation:

$$C5 > \frac{4}{2\pi \times R4 \times 0.1 \times F_{OSC}}$$

3. If the  $C_{\text{OUT}}$  ESR zero is less than half of the switching frequency, use C7 to cancel the ESR zero:

$$C7 = \frac{C_{OUT} \times R_{ESR}}{R4}$$

#### **External Boost Diode Selection**

For 5V input applications, it is recommended to add an external boost diode. This helps improving the efficiency. The boost diode can be a low cost one, such as 1N4148.

This diode is also recommended for high duty cycle applications.

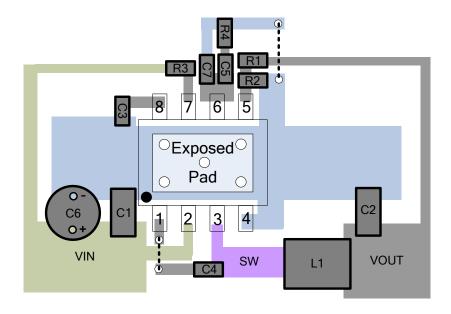

#### **PCB Layout Recommendation**

The device's performance and stability are dramatically affected by PCB layout. It is recommended to follow these general guidelines shown as below:

- Place the input capacitors and output capacitors as close to the device as possible. The traces which connect to these capacitors should be as short and wide as possible to minimize parasitic inductance and resistance.

- 2. Place  $V_{\text{IN}}$  capacitors close to the  $V_{\text{IN}}$  pin.

- 3. Place feedback resistors close to the FB pin.

- Place compensation components close to the COMP pin.

- 5. Keep the sensitive signal (FB, COMP) away from the switching signal (SW).

- 6. The exposed pad of the package should be soldered to an equivalent area of metal on the PCB. This area should connect to the GND plane and have multiple via connections to the back of the PCB as well as connections to intermediate PCB layers. The GND plane area which connects to the exposed pad should be maximized to improve thermal performance.

- 7. Multi-layer PCB design is recommended.

# **Application Information (Continued)**

Figure 18. FR9872 Recommended Layout Diagram

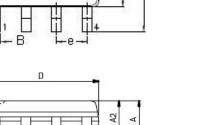

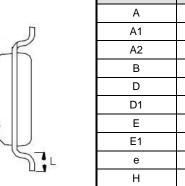

### **Outline Information**

#### SOP-8 (Exposed Pad) Package (Unit: mm)

| SYMBOLS                            | DIMENSION IN MILLIMETER |      |  |  |

|------------------------------------|-------------------------|------|--|--|

| UNIT                               | MIN                     | MAX  |  |  |

| Α                                  | 1.25                    | 1.70 |  |  |

| A1                                 | 0.00                    | 0.15 |  |  |

| A2                                 | 1.25                    | 1.55 |  |  |

| В                                  | 0.31                    | 0.51 |  |  |

| D                                  | 4.80                    | 5.00 |  |  |

| D1                                 | 3.04                    | 3.50 |  |  |

| E                                  | 3.80                    | 4.00 |  |  |

| E1                                 | 2.15                    | 2.41 |  |  |

| е                                  | 1.20                    | 1.34 |  |  |

| Н                                  | 5.80                    | 6.20 |  |  |

| L                                  | 0.40                    | 1.27 |  |  |

| Note: Followed From JEDEC MO 042 F |                         |      |  |  |

Note: Followed From JEDEC MO-012-E.

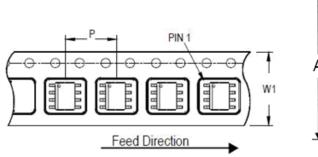

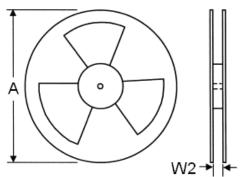

### **Carrier Dimensions**

| Tape Size   Pocket Pitch |        | Reel Size (A) |     | Reel Width | Empty Cavity | Units per Reel |

|--------------------------|--------|---------------|-----|------------|--------------|----------------|

| (W1) mm                  | (P) mm | in            | mm  | (W2) mm    | Length mm    |                |

| 12                       | 8      | 13            | 330 | 12.4       | 400~1000     | 2,500          |

Life Support Policy

Fitipower's products are not authorized for use as critical components in life support devices or other medical systems.

13 FR9872-1.3-MAR-2012